電源設計在電子系統中具有至關重要的地位,其質量和穩定性直接影響整個系統的性能、可靠性和穩定性。

簡要來說,主要有以下作用:

穩定供電:電源設計的主要目標之一是提供穩定、可靠的電源電壓和電流。在電子系統中,許多元件和器件對于電源的穩定性都非常敏感,不穩定的電源可能導致系統工作不正常或損壞。

系統性能:電源的質量直接影響系統的性能。良好的電源設計可以確保系統在各種工作條件下都能夠提供足夠的電力,以滿足各個組件的要求,從而保障系統的性能和效率。

抑制噪聲:電源中的噪聲可能對系統的正常運行産生負面影響。通過適當設計電源,特別是使用去耦電容和濾波器等元件,可以有效減小電源中的噪聲,確保信號質量和系統穩定性。

系統可靠性:電源問題是導致電子系統故障的常見原因之一。穩定的電源設計可以降低系統發生故障的概率,提高系統的可靠性和穩定性。

適應性:不同的應用場景可能對電源的要求不同,有些需要高電流輸出,有些需要高效率,有些需要低功耗。電源設計需要根據具體應用的要求進行調整,以滿足系統對電源的不同需求。

節能和效率:良好的電源設計可以提高系統的能效,減小功耗,降低能源消耗。這對于移動設備、電池供電設備以及對能源效率要求較高的應用尤爲重要。

避免電磁幹擾:電源設計還需要考慮電磁兼容性(EMC)和電磁幹擾(EMI)的問題,以防止電源本身産生幹擾或受到外部幹擾。

1.

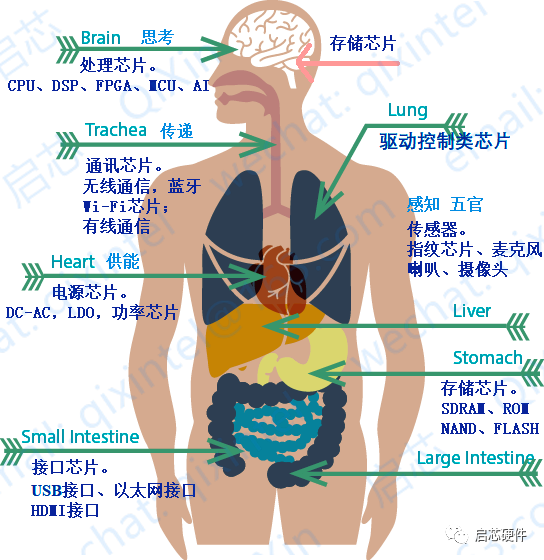

下面這張圖是我設計的一個對照圖。人體器官對應常見電路的功能模塊,我覺得這樣比較形象。比如,大腦就對應常用的電路系統中的CPU部分,肚子呢?吃東西的,就相當于存儲部分。而我們的心髒不停的跳動,泵血,當然就相當于電路系統中的電源了。

2. 退耦電容的工作邏輯

因此,本文不會展開聊,只是關注一個小細節,就是電源中的退耦電容。

這往往又是電源設計中最容易被忽略的地方。很多人搞ARM,搞DSP,搞FPGA,乍一看似乎搞的很高深,但未必有能力爲自己的系統提供一套廉價可靠的電源方案。退耦電容是電源電路不可或缺的部分,我們從退耦電容一個作用點說起---退耦電容的小池塘作用。

爲簡單清晰的說明這個問題,我做了下圖。左邊是水庫,右邊是小池塘和玉米莊稼地。工作邏輯是這樣的:雖然直接用水庫裏的水灌溉玉米地也是可以的,但是由于距離太遠,遠水解不了近渴,所以莊稼地很容易幹死。因此,通常情況下,在玉米地附近,會配套的開發出,小池塘,用作零時的水源供應。

詳細來說,當玉米地需要灌溉時,從旁邊的小池塘中,可以直接取水,保證玉米的穩定生長。而小池塘中,如果缺水,可以從水庫中調水過來,因此池塘是有存儲功能的。這樣就可以保證整個系統的穩定工作。

對照來說,水庫就相當于式電路系統中的電源供應模塊,小池塘就相當于是退耦電容,而玉米地就是工作的芯片,處理器等。芯片穩定工作,需要穩定的供電,但是如果芯片的電壓需求波動時,電源來不及及時處理,此時,退耦電容就可以充當臨時電池,來補充需要的電源。以保證系統的穩定工作。

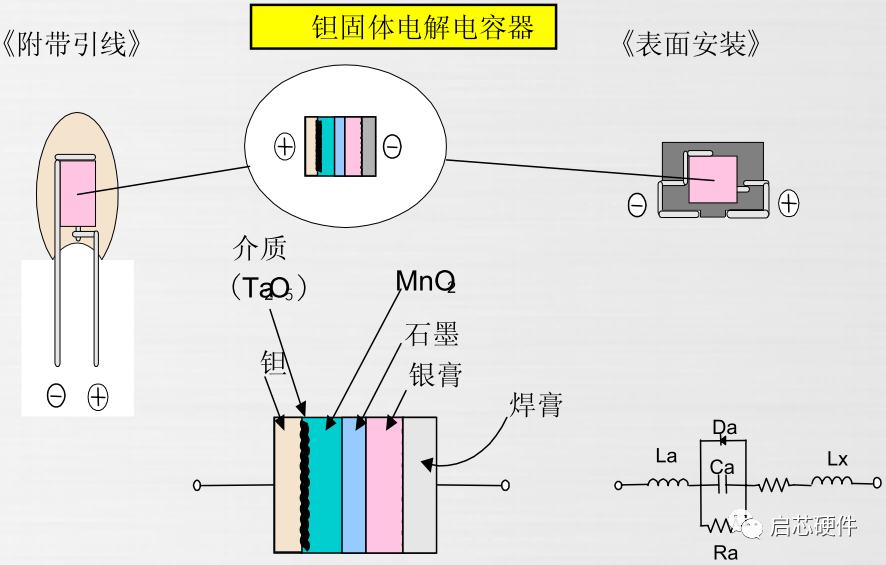

很多人對電容的概念大多還停留在理想的電容階段,一般認爲電容就是一個C。卻不知道電容還有很多重要的參數。實際的電容可以等效成下面的電路形式:

C:電容容值。一般是指在1kHz,1V 等效AC電壓,直流偏壓爲0V情況下測到的,不過也可有很多電容測量的環境不同。但有一點需注意,電容值C本身是會隨環境發生改變的。

ESL:電容等效串聯電感。電容的管腳是存在電感的。在低頻應用時感抗較小,所以可以不考慮。當頻率較高時,就要考慮這個電感了。舉個例子,一個0805封裝的0.1uF貼片電容,每管腳電感1.2nH,那麽ESL是2.4nH,可以算一下C和ESL的諧振頻率爲10MHz左右,當頻率高于10MHz,則電容體現爲電感特性。

ESR:電容等效串聯電阻。無論哪種電容都會有一個等效串聯電阻,當電容工作在諧振點頻率時,電容的容抗和感抗大小相等,于是等效成一個電阻,這個電阻就是ESR。因電容結構不同而有很大差異。鋁電解電容ESR一般由幾百毫歐到幾歐,瓷片電容一般爲幾十毫歐,钽電容介于鋁電解電容和瓷片電容之間。

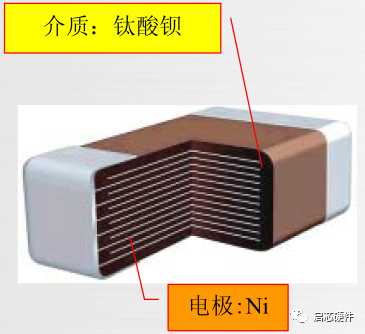

2)瓷片電容存放電靠的是物理反應,因而具有很高的響應速度,可以應用到上G的場合。不過,瓷片電容因爲介質不同,也呈現很大的差異。性能最好的是C0G材質的電容,溫度系數小,不過材質介電常數小,所以容值不可能做太大。而性能最差的是Z5U/Y5V材質,這種材質介電常數大,所以容值能做到幾十微法。

3)钽電容無論是原理和結構都像一個電池。

首先,要說的是钽電容其實是電解電容的一種,這個很多人都不知道。钽電容擁有體積小、容量大、速度快、ESR低等優勢,價格也比較高。決定钽電容容量和耐壓的是原材料钽粉顆粒的大小。顆粒越細可以得到越大的電容,而如果想得到較大的耐壓就需要較厚的Ta2O5,這就要求使用顆粒大些的钽粉。所以體積相同要想獲得耐壓高而又容量大的钽電容難度很大。钽電容需引起注意的另一個地方是:钽電容比較容易擊穿而呈短路特性,抗浪湧能力差。因此,雖然钽電容有很多優點,但由于某些場合容易被擊穿,因此應用的時候,一定要多加考慮。很多時候,我們避免用钽電容。

3. 電源設計中電容的作用

在電源設計應用中,電容主要用于濾波(filter)和退耦/旁路(decoupling/bypass)。

濾波主要指濾除外來噪聲

而退耦/旁路是減小局部電路對外的噪聲幹擾。

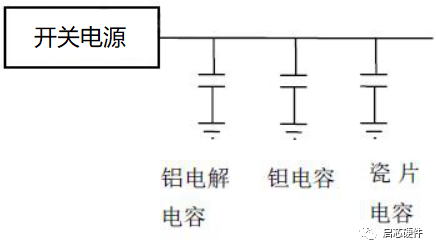

一般濾波主要使用大容量電容,對速度要求不是很快,但對電容值要求較大。一般使用鋁電解電容。

浪湧電流較小的情況下,使用钽電容代替鋁電解電容效果會更好一些。一般來說,作爲退耦的電容,必須有很快的響應速度才能達到效果。

另外,退耦電容需要滿足兩個要求,一個是容量需求,另一個是ESR需求。

也就是說一個0.1uF的電容退耦效果也許不如兩個0.01uF電容效果好。而且,0.01uF電容在較高頻段有更低的阻抗,在這些頻段內如果一個0.01uF電容能達到容量需求,那麽它將比0.1uF電容擁有更好的退耦效果。通常,電源的濾波中,會考慮將不同容值得得電容並聯起來,以形成一個低阻抗的坑,達到更好的濾波效果,讓系統工作更穩定。

4.總結:

深入理解去耦電容:瞬態響應:去耦電容的主要功能之一是在瞬態負載變化時提供電流,以確保穩定的電源電壓。例如,當集成電路需要瞬時高電流時,去耦電容能夠滿足這一需求,防止電源電壓下降。

高頻噪聲過濾:去耦電容能夠過濾電源中的高頻噪聲,確保供電電壓的紋波較小。這對于模擬和數字電路都是至關重要的,因爲它可以提高系統的性能和穩定性。

電源穩定性:在整個電源系統中放置去耦電容有助于維持電源穩定性。這對于避免電源電壓的劇烈波動以及電源回路的互相影響非常重要。

電感耦合:在長電源線路上,電感可能導致電源電壓的波動。去耦電容通過提供額外的電荷來抵消電感的影響,有助于維持電源電壓的穩定性。

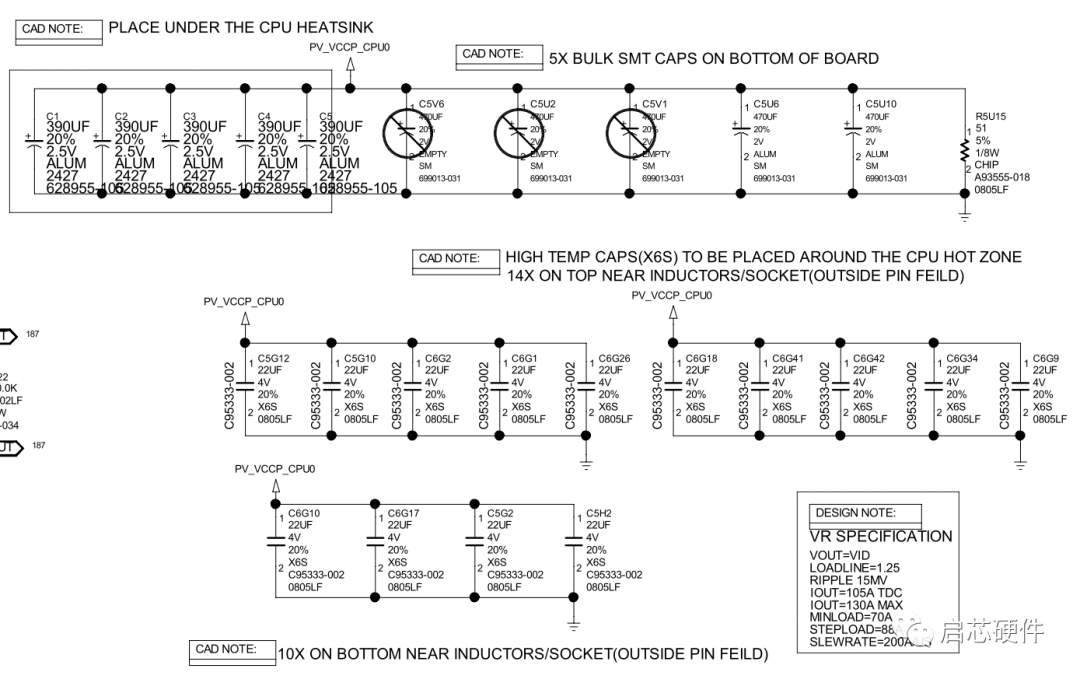

5.應用實例:IC去耦:在集成電路的電源引腳附近放置去耦電容,以確保在IC需要瞬時電流時能夠得到滿足。這對于數字和模擬電路都是至關重要的。

電源模塊:在電源模塊的輸入和輸出端放置去耦電容,以平滑電源電壓,提高瞬態響應,並減小輸出中的高頻噪聲。

電源平面設計:在多層板設計中,通過在電源平面上分布去耦電容,可以確保整個板上的電源穩定性。這對于大型系統和高頻應用尤爲重要。

RF應用:在射頻(RF)電路中,去耦電容用于提供電源穩定性,並過濾高頻噪聲,確保射頻信號的准確傳輸。

時鍾電路:在時鍾電路中,去耦電容有助于維持時鍾信號的穩定性,防止時鍾抖動和相位噪聲。