一、IBM Telum芯片概要

IBM 在2021年 HotChips 上發布了 IBM Telum 處理器;Telum 成爲下一代 IBM Z 和 LinuxONE 系統的中央處理器芯片。

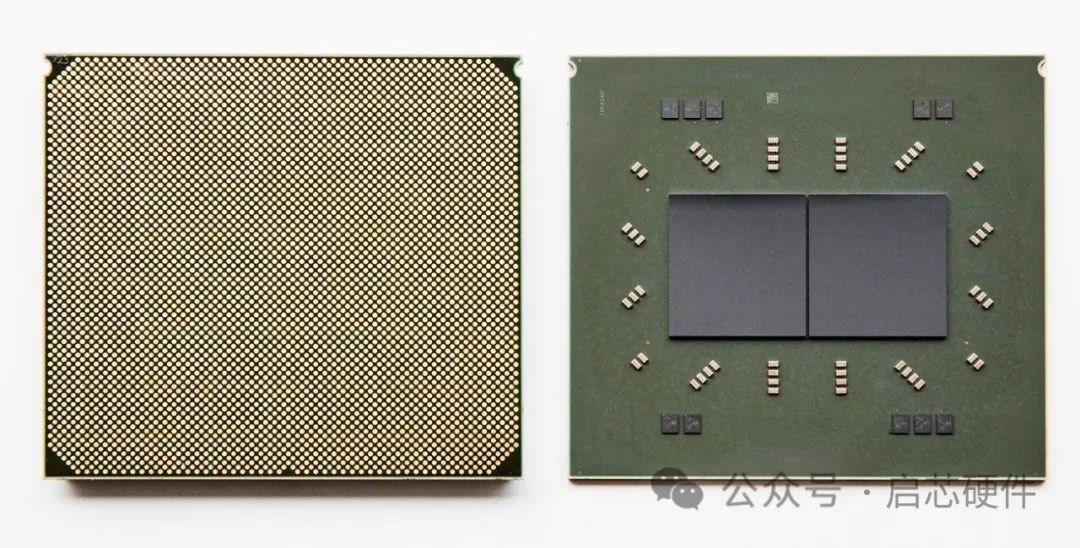

Telum 比 z15 更簡單——它是一款基于三星 7nm 工藝構建的八核處理器,每個封裝上組合了兩個處理器(類似于 AMD Ryzen 的小芯片方法)。

前身 IBM z15 芯片旨在爲 IBM Z 和 LinuxONE 系統提供業界領先的七個 9 可用性。Telum 旨在通過關鍵創新進一步提高可用性,包括重新設計的 8 通道內存接口,能夠承受整個通道或 DIMM 故障,並設計用于透明地恢複數據而不影響響應時間。

Telum 添加了新的集成 AI 加速器,每個芯片的計算能力超過 6 TFLOPs。每個核心都可以訪問AI加速器,並且可以動態地利用整個計算能力來最大限度地減少推理延遲。由于集中式加速器架構直接連接到緩存基礎設施,Telum 旨在爲響應時間敏感的工作負載實現極低延遲的推理。計劃系統支持高達 200 TFLOP,AI 加速還旨在擴展以滿足最苛刻的工作負載的要求。

Telum 的工作原理

在諸如CPU之類的傳統計算系統中,計算是通過在存儲器和處理器之間重複傳輸指令和數據來執行的。但人工智能工作負載的計算要求要高得多,並且需要處理大量數據。因此,當您將 AI 融入應用程序工作流程時,擁有一個由 CPU 和 AI 內核組成的異構系統至關重要,這些系統緊密集成在同一芯片上,以支持極低延遲的 AI 推理。

Telum 正是實現了這一目標,除了傳統的 CPU 性能之外,還爲未來的 IBM 系統提供了專用的 AI 資源。CPU 內核可有效用于通用軟件應用程序,AI 內核可高效運行深度學習工作負載,並且兩種類型內核的緊密耦合有助于促進快速數據交換。

Telum 沿襲了 IBM 的全棧系統設計方法的曆史,即針對客戶最關鍵的工作負載共同優化芯片技術、硬件、固件、操作系統和中間件。借助 Telum,客戶每秒可以處理數以萬計的人工智能交易。

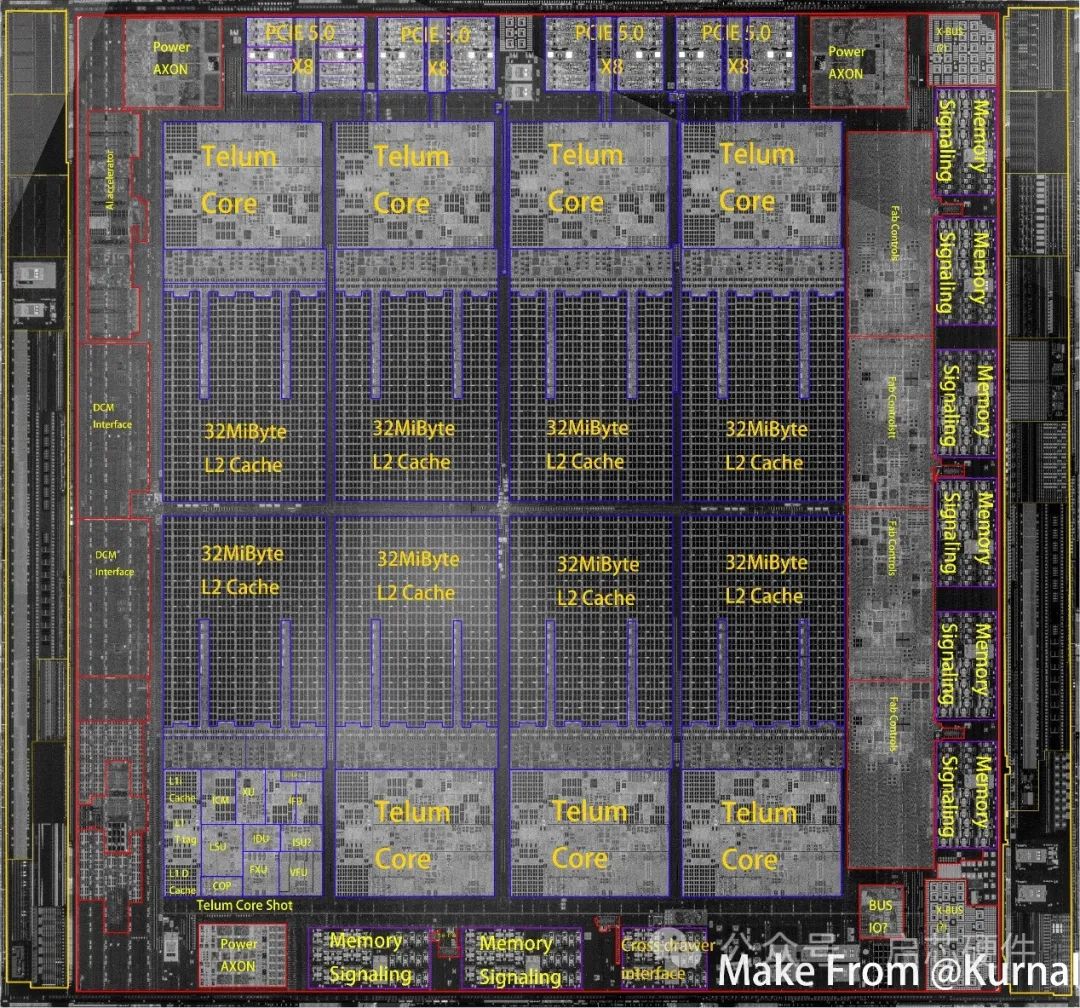

二、Telum的 die floorplan 基本介紹

IBM Telum芯片的floorplan如下圖所示

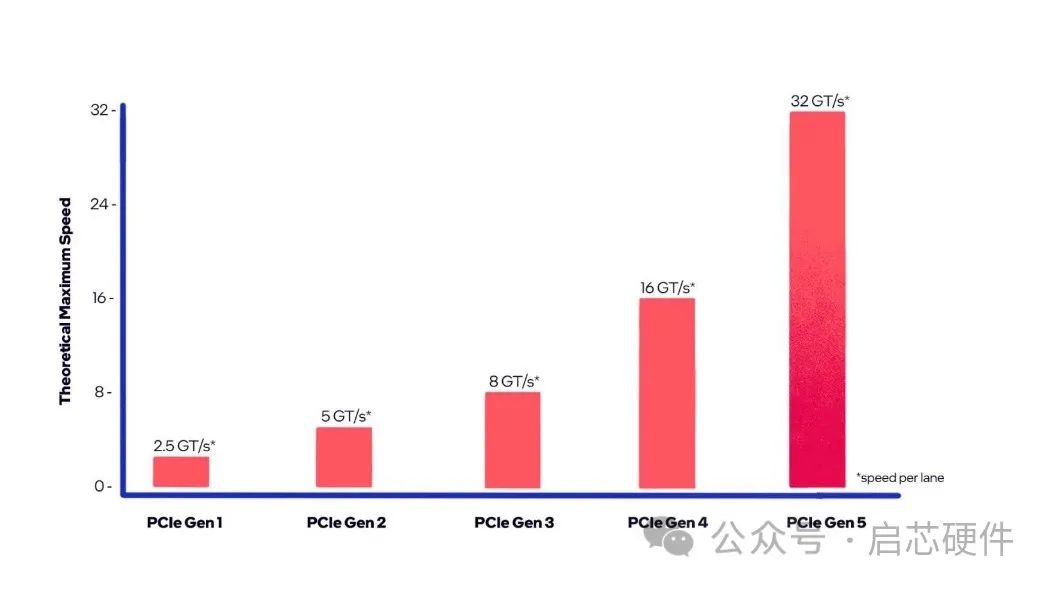

1.PCIe 模組,最上方爲PCIe 5.0, X8規格,一共四個,理論上能提供的傳輸速率爲32GT/sx8x4=1024GT/s

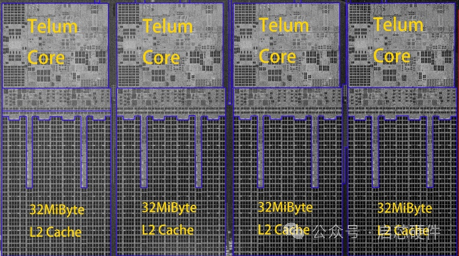

2.Telum core和緩存。正下方是8組telum core和L2緩存,采用4上4下的mirror擺放,組成8 core+8 cache的結構。值得注意的是有一個超大的L2 Cache, 達到了32MB, 要知道一般同類芯片L2 可能只有1MB左右。

3.DDR模組。其中一個如下圖,一共4組,爲DDR5規格。

Telum是一種新一代的芯片,能看出一些 power 的影子,但是確實不完全是 power,偏向于銀行和加密需求。它的緩存設計取消了L3和L4,用巨大的L2代替,可以將數據存儲在其他核心、基板、組或單元的空閑L2內。除此之外,Telum還擁有4通道ddr5、x8x4pcie5.0和一堆AI加密單元。

高速緩存是每個微處理器的關鍵設計組件,對處理器的整體性能影響巨大。緩存就像存儲櫃,可以在處理器的前門存儲數據,或者提前緩存數據。

這對于當今運行速度如此之快(通常以許多千兆赫的速度)的處理器來說尤其重要,以至于每當系統需要等待數據時,寶貴的時鍾周期就會被浪費。

Telum 取消了 L3,L4,用巨大的 L2 來代替,這樣設計會導致其緩存具有巨大的訪問延遲,但是 telum 很神奇,其將以前放置在 L3 的數據放在其余空余核心的 L2 內,L4 同理,導致其意義上,一個 chip 物理有 256M 的 L2 (8X32), 但是單個核心可以讀取核心外的 32M l2,256M L3,以及一整個複合體(整個 ibm z16?單元)的 32mx8 核 x2(2die 封裝一個 sub)x16 的 8GB 的 L4,說明白點,一個核心數據存不下了可以放在其他核心,不同基板,甚至不同組或者不同單元的 L2 內,只要是空閑的。

三、Telum的 dieshot細節分析

Telum微處理器包含 8 個處理器核心,主頻超過 5GHz,每個核心均由重新設計的 32MB 專用二級緩存支持。二級緩存交互形成256MB虛擬三級緩存和2GB四級緩存。除了處理器內核本身的改進之外,每個內核的緩存比 z15 一代增長了 1.5 倍,旨在顯著提高 IBM 在下一代 IBM Z 系統中提供的每線程性能和總容量。Telum 的性能改進對于複雜交易系統的快速響應時間至關重要,尤其是在實時人工智能推理的增強下。

該芯片還包含 220 億個晶體管和 17 個金屬層上 19 inch的走線。Telum由三星制造,采用7nm EUV技術節點開發。

IBM 院士Christian Jacobi表示:“我們對 Telum 芯片所做的就是完全重新設計了這些緩存的工作方式,使更多的數據比過去更靠近處理器核心。” IBM zSystems 系統架構和設計首席技術官。“爲此,我們將二級緩存增加了四倍。我們現在擁有 32 MB 的二級緩存。”

L2 緩存的這個大小與大多數其他服務器芯片形成鮮明對比,其他服務器芯片的緩存大小約爲半兆字節或 1 MB。爲了使這個更大的 L2 緩存有效工作,IBM 優化了訪問模式以及處理器核心如何訪問非常大的 32 MB 緩存(八個核心爲 256 MB),從而使其具有極低的延遲。

“我們不再受控制邏輯的限制,控制邏輯要確定數據在緩存中的實際位置,然後將請求發送到緩存的正確扇區並緩慢移動數據,”Jacobi 說。“我們的設計方式是,我們真正只受到電傳輸延遲的限制,以獲取數據、觸發從陣列中讀取數據,然後將其流回需要的地方。”

四、總結

Telum 芯片之前的一代芯片采用四級高速緩存:最接近的一級高速緩存是一級 (L1),下一級是二級 (L2),依此類推,直到達到四級 (L4)。傳統上,緩存層次結構是在芯片上構建 L1、L2 和 L3,而 L4 則在芯片外構建。每個級別的大小都會隨著您的推移而增加,並且它們距離處理器引擎本身越遠,延遲也會增加。

IBM Telum Dieshot,圖片來自 IBM 官網,制作 / 繪畫來自 Kurnal