這次Pura70系列除了標准版之外,其它三款機型皆搭載了全新的處理器麒麟9010。單看處理器型號的話,結合以往麒麟處理器命名的規則,一般會認爲這就是個麒麟9000S的超頻版。

結果處理器的CPU規格一出來,卻顯示大核主頻大幅降低了!至于中核與小核的主頻,則是略微提升了一點點,此外其也具備和麒麟9000S一樣的超線程設計。

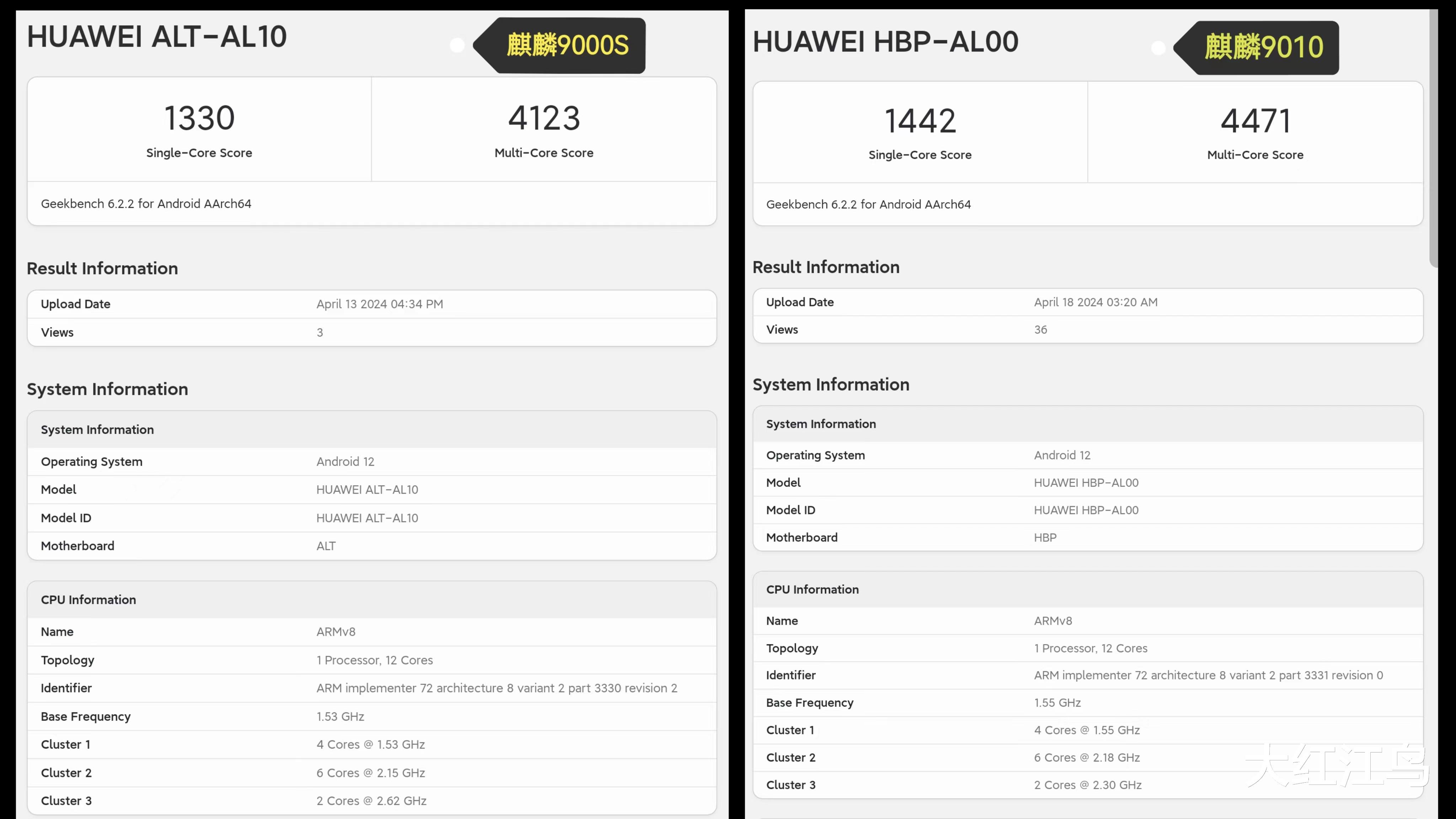

GPU部分則依然是麒麟9000S所采用的那款 Maleoon 910,所以這代唯一的變化就是CPU部分。通過CPU性能的跑分可知(下圖所示),大核主頻雖然降低了,但性能卻上升了!

很明顯這並非麒麟9000S的降頻版,而是CPU核心微架構得到升級的一款全新處理器!GB6跑分中CPU單核性能上升了8.4%,多核性能也同樣是提升了8.4%。

也就是說單看GB6跑分的話,麒麟9010的大核IPC是有23%之提升的,下面再看其大核的整數和浮點跑分之IPC有何變化。

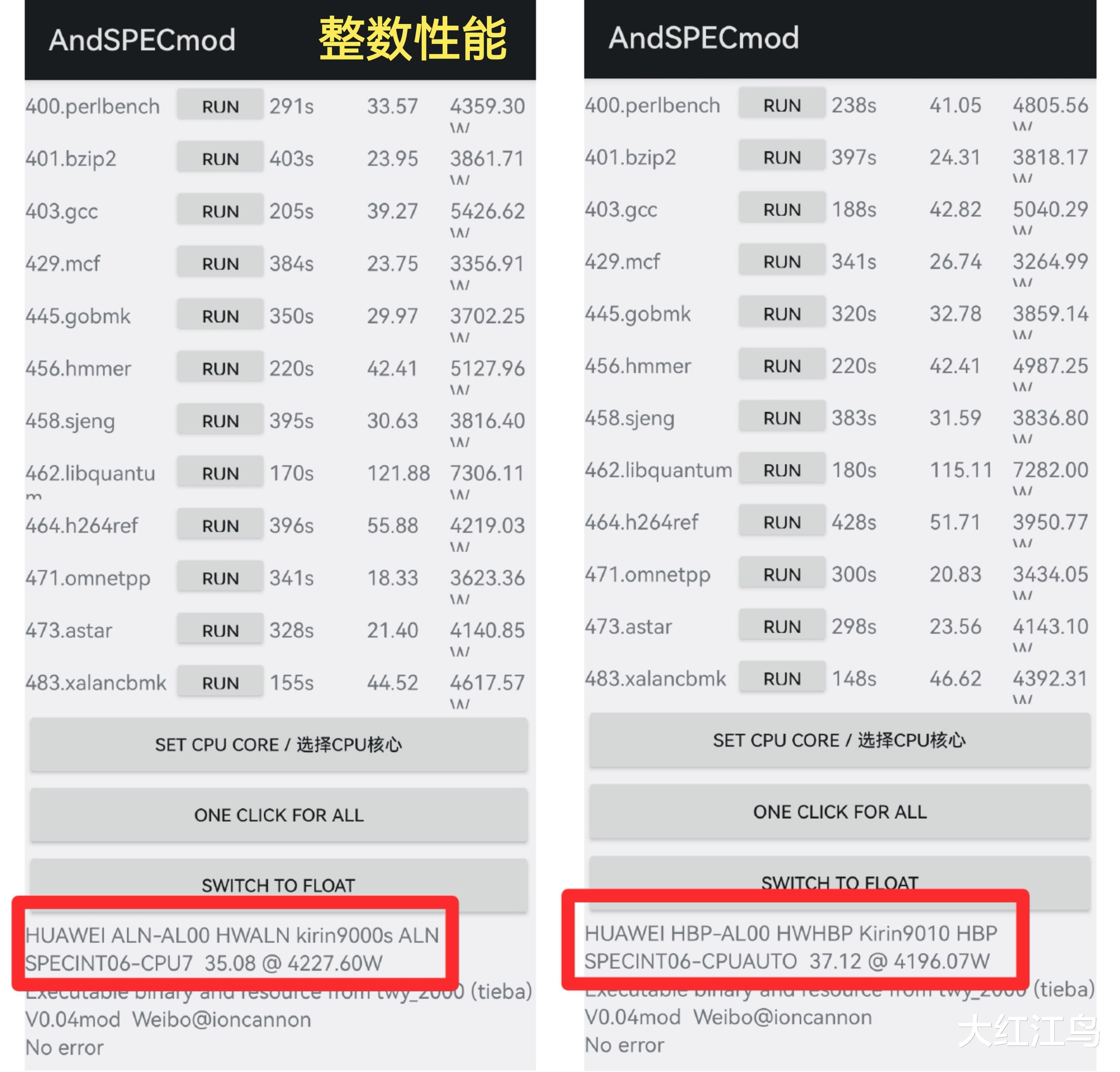

如下圖所示,麒麟9010較麒麟9000S的大核整數性能,在相同功耗情況下有5.8%的優勢,換言之其能效更高些;若再結合兩者主頻的區別,就意味著其整數IPC進步了20%!

下圖的大核浮點性能部分,麒麟9010較麒麟9000S具有7.25%的優勢,而且功耗表現也很一致——能效方面提升明顯;結合兩者主頻的區別,其浮點IPC就進步了21.7%。

總結就是,這次麒麟9010的CPU大核IPC性能,較麒麟9000S是有20%以上之大幅提升的。而且因爲頻率定得比較低,所以其能效表現較麒麟9000S也有5%以上的提升。

從這也可以看出,在制程工藝受限制的情況下爲了改善CPU能效表現,華爲想出了微架構大幅升級但卻降低主頻的辦法,最終在相同功耗表現下做到了性能有所提升。

之前麒麟9000S的CPU大核,在IPC性能方面整體是略弱于骁龍888的;而這次麒麟9010的CPU大核,其整數IPC與骁龍8+ Gen1一致,而在浮點IPC上則實現了超越!

也就是說這次麒麟9010的CPU自研大核微架構,在性能設計方面是比較接近骁龍8+ Gen1之X2超大核微架構的,下面就從微架構方面去探究兩者有什麽相似性。

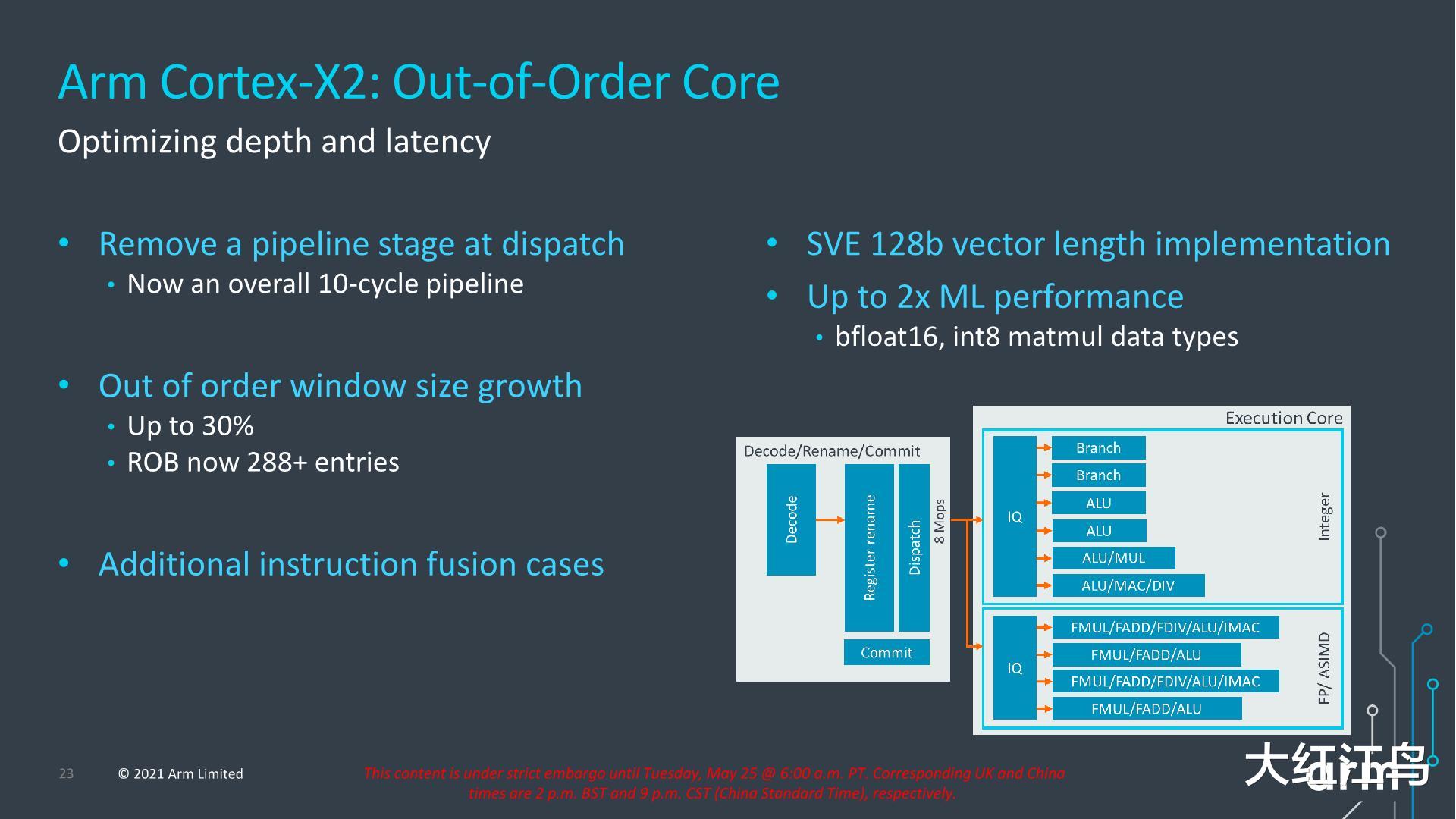

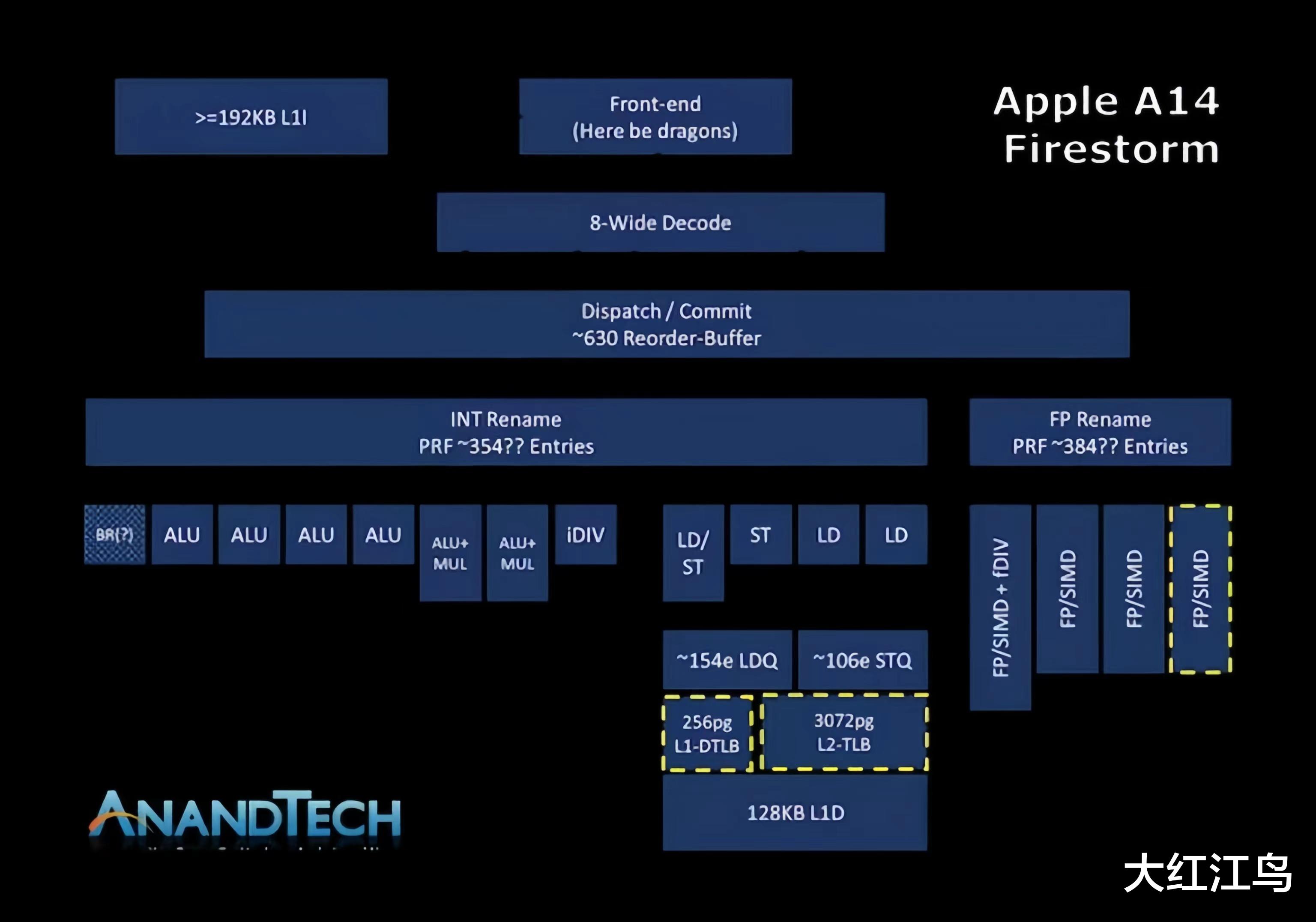

先從Cortex-X2架構入手,從下圖可知其前端爲8發射寬度,亂序窗口的ROB深度爲288,後端整型部分擁有4個整數執行單元,流水線管道從X1的11級減少到了10級。

至于麒麟9010的大核微架構,從已知的信息來看,其與X2微架構只有8發射對得上;其它的諸如8解碼寬度、6個整數執行單元,都要大于X2的6解碼寬度和4整數執行單元。

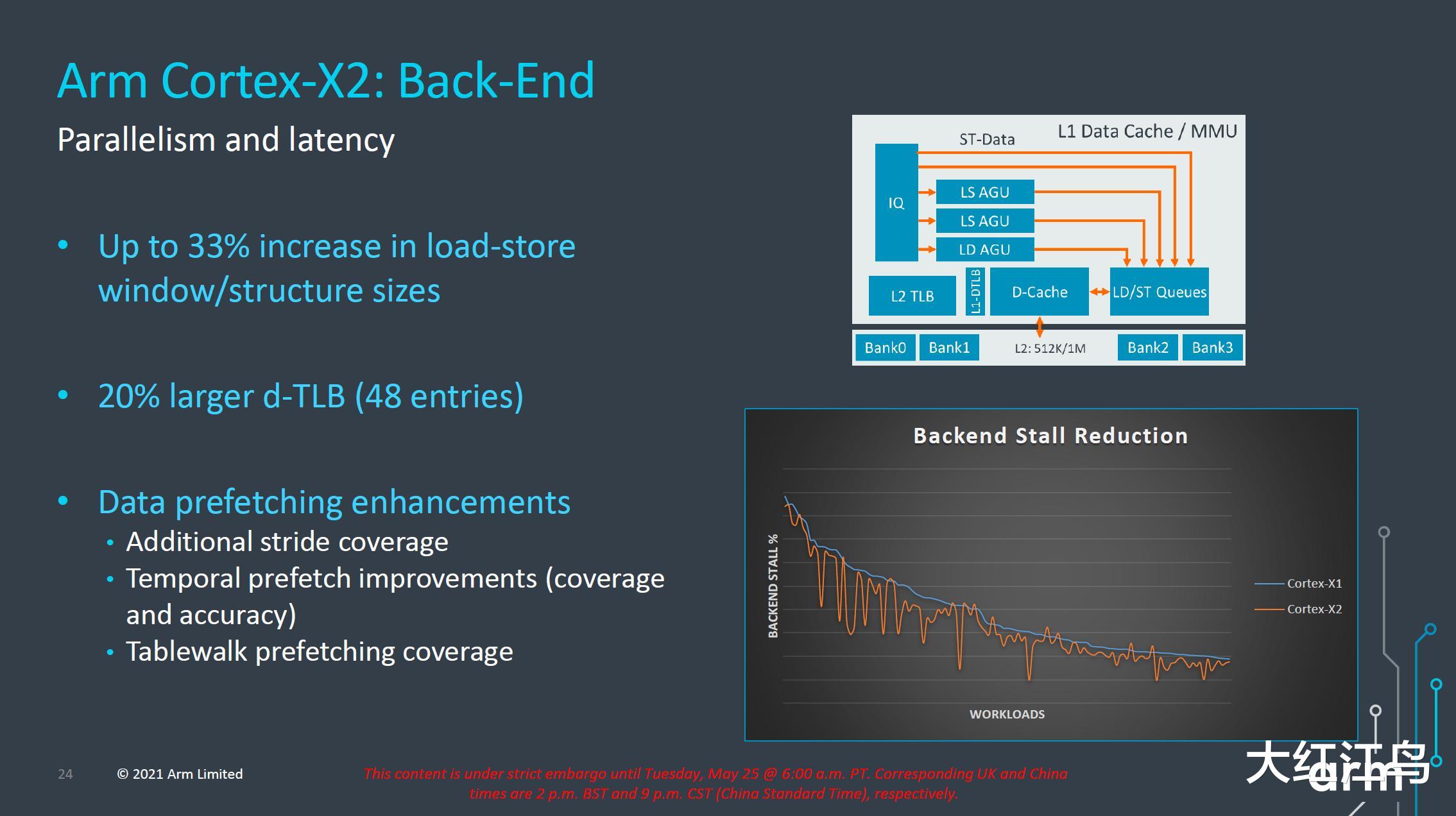

另外在緩存系統方面麒麟9010和骁龍8+ Gen1也很像,兩者在前端L1指令緩存、後端L1數據緩存、L2緩存等方面皆保持一致,但在L3緩存和SLC緩存等方面麒麟9010還沒有確切數值。

由于L3緩存和SLC緩存影響的主要是大核的能效表現,所以在緩存系統方面兩者算是把變量控制住了;也就是說,在前端和後端都更寬的情況下,麒麟只有浮點IPC超越了X2。

之所以會出現這種情況,其根因還是與制程工藝有關。另外,說到這就要將微架構的方向看到果子那邊了,因爲華爲在新麒麟的微架構設計路線上,與果芯路線不謀而合。

例如麒麟9010大核的8解碼8發射前端寬度,與蘋果A14的前端寬度一致,同時兩者後端的整數單元數量也一樣爲6個。但是,果子那邊緩存系統整體優勢極大,且ROB深度高達630!

最終,A14的大核整數IPC性能,比麒麟9010的大核高出了31%!所以,前端後端的寬度只是一個前提,若要順利實現更好的指令級並行性,還得學果子將該堆的料全都堆上。

最後,還得回到一切的症結所在:制程工藝受限制情況下,華爲的微架構設計能力受到嚴重制約,爲了在性能和能效之間保持一個平衡,最終才有了麒麟9010的CPU架構現狀。

例如,假如華爲要學果子將緩存系統和ROB深度堆上去,那就要增加大量的晶體管,但這樣做又會推高成本、增加功耗、降低良率。而解決方法只有一個,那就是升級制程工藝。

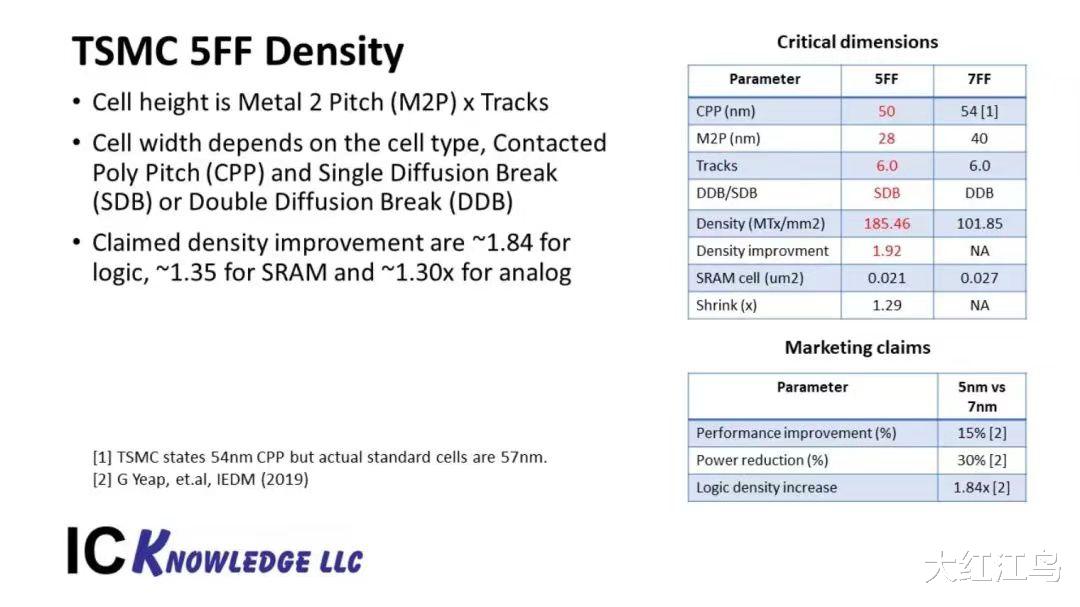

之前在制程升級方面如下圖所示,從台積電7nm工藝升級到台積電5nm工藝,可以提高約1.84倍的邏輯密度和1.35倍的SRAM密度,同時還能降低30%的同頻功耗,收益極其顯著。

其中,提升幅度最大的邏輯密度,可以將SoC內各個功能模塊的電路尺寸大幅壓縮,這就意味著在相同面積內可以堆更多晶體管,或者在相同晶體管數量下大幅壓縮芯片面積。

而SRAM密度則與各級緩存相關,可以在之前同樣面積下塞入更大容量的高速緩存;又由于緩存系統與能效表現息息相關,所以這方面堆到位情況下性能設計的余裕空間就很大了。

總的來說這兩方面密度大幅提升的結果就是:微架構IPC性能提升的空間極大,因爲能夠在芯片面積不變或者變小的情況下塞進更多晶體管,其中既有提高性能的也有改善能效的。

解析到這裏,麒麟9010大核背靠全新微架構,主頻卻還是降低至2.3GHz的原因已基本明了,本質上就是制程工藝限制了微架構的設計空間——性能大幅提升與能效表現不可兼得。

假如能有對應的工藝條件,那麽麒麟9010的大核微架構就可以像基于台積電5nm工藝打造的蘋果A14一樣,添加足夠的晶體管去堆緩存和ROB,這樣便能縮小兩者IPC性能的差距。

最後的問題就是,華爲和蘋果的CPU微架構路線,怎麽會不謀而合呢?這其實也挺巧的,華爲是迫不得已將電腦端的鲲鵬自研核心延伸至麒麟,而蘋果則是從A系列順延至M系列。

兩岸猿聲啼不住,輕舟已過萬重山!